# Examination of Some Basic Electrical Properties of Au/p-Si/AI, Au/GO/p-Si/AI and Au/Au-RGO/p-Si/AI structures

Merve ODABAŞ<sup>1</sup>, Ahmet TAŞER<sup>2</sup>, Züleyha KUDAŞ<sup>3</sup>, Betül GÜZELDİR<sup>4</sup> and Mustafa SAĞLAM<sup>5</sup>

**Abstract**— To examine the effects of GO and Au-RGO interface layers on Schottky diode parameters, Au/p-Si/Al, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al structures were fabricated at room temperature, respectively. Graphene oxide (GO) and reduced graphene oxide with Au nanoparticles (Au-RGO) thin films were grown on polished surfaces of chemically cleaned p-Si semiconductor parts by the spin coating technique at 1000 rpm for 1 min, respectively. The GO and Au-RGO were synthesized using graphite powder by modified Hummer's method. Before the GO and Au-RGO thin films were deposited, the ohmic contacts were made to p-Si semiconductors with Al metal. Au metal on the GO, Au-RGO thin films and p-Si was evaporated in vacuum and thus the Au/p-Si/Al, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al structures were obtained. The diameter of the circular gold contacts was determined as 1 mm. By using the current-voltage measurements taken at room temperature, rectifying ratio, interface state density and series resistance values of diodes with and without interfacial layer were calculated by means of thermionic emission method. The results were compared and interpreted.

Index Terms— Graphene oxide, interface state density, rectifying ratio, reduced graphene oxide, thermionic emission, Schottky diode, series resistance.

\_ \_ \_ \_ \_ \_ \_ \_ \_ \_

#### **1** INTRODUCTION

NOWADAYS with developing technology, the use of semiconductor based electronic circuit elements has also developed rapidly.

The most common of these circuit elements is the metalsemiconductor structures obtained by contacting the metal with the semiconductor. One of the most interesting features of a metal semiconductor interface is the Schottky barrier height (SBH), a measure of the mismatch of energy levels for the majority carriers in the metal semiconductor interface. SBH controls the electronic transitions from the metal interface to the semiconductor interface and is therefore vital to the successful operation of any semiconductor device [1]. The most effective method for the controlled exchange of SBP is to add a thin layer between the metal and the semiconductor [2].

Gaphene, two-dimensional structure of sp2 -hybridized carbon, exhibits unique properties which have amazing the scientific community and has made it the major research topics in the last decade [3]. Graphene oxide (GO) is a singleatomic layered material consisting of carbon, oxygen and hydrogen-terminated carboxylic or enol functionalities obtained by the oxidation of graphite crystals. The reduced graphene oxide (RGO) is chemically derived graphene [4].

In this study, Graphene oxide (GO) and reduced graphene oxide with Au nanoparticles (RGO) thin films were used as the interface layer and some basic electrical properties of the obtained metal semiconductor structures have been studied.

## 2 EXPERIMENTAL

\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_

In order to clean the chemical oils and impurities on the p-Si semiconductor used in this study, washing was carried out for 10 minutes in acetone and methanol, respectively. After this stage, rinsed with deionized water p-Si semiconductor, known as organic RCA1: (H<sub>2</sub>O: H<sub>2</sub>O<sub>2</sub>: NH<sub>3</sub>; 6:1:1) was subjected to a treatment to stand for 10 minutes at 60 °C in the chemical cleaning process. The p-Si semiconductor, which was held for 30 seconds in dilute HF: (H<sub>2</sub>O: HF; 10:1) after the RCA1 procedure and than second cleaning procedure was called RCA2: (H<sub>2</sub>O: H<sub>2</sub>O<sub>2</sub>: HCl; 6:1:1) and was processed a treatment known as metallic cleaning. The samples were kept at 60 °C for 10 minutes at RCA2. After the RCA2 treatment, the p-Si semiconductor was washed thoroughly with deionized water for 30 seconds in diluted HF and then passed through a deionized water for 15-20 min. Finally, the chemical cleaning process was completed by drying with pure nitrogen gas.

Cleaned p-Si semiconductor ohmic contact process in the first stage was carried out by evaporating Al metal directly to one surface at 5x10<sup>-7</sup> torr pressure and in the second stage the p-Si semiconductor was annealed at 580 °C for 3 minutes in pure nitrogen gas flow. Thus, our p-Si/Al-ohmic contact was obtained, this semiconductor was divided into 3 equal parts. Before the rectifier contact metallization process, the surfaces of each of the three parts to be contacted with the rectifier were subjected to chemical cleaning for 30 s HF: (H<sub>2</sub>O: HF; 10: 1).

Then, the Au/p-Si/Al reference rectifier contact was obtained by thermally evaporating Au metal to the first part with the help of a mask with circular contact area 7,85x10-3 cm2 at 5x10-7 torr pressure.

Thin films of GO and Au-RGO synthesized using graphite powder by modified Hummer method [5] were coated on the

<sup>1.3,4,5</sup> Faculty of Sciences, Atatürk University, Erzurum, Turkey, E-mail: merveodabas29@hotmail.com, zkudas@atauni.edu.tr, bgüzeld-

ir@atauni.edu.tr, msaglam@atauni.edu.tr

<sup>&</sup>lt;sup>2</sup>Patnos Vocational School, İbrahim Çeçen University, Ağri, Turkey, E-mail: ataser@agri.edu.tr

rectifier contact surface of both parts by spin coating method. Thermally evaporated Au metal by a mask with circular contact area 7,85x10-3 cm2 at 5x10-7 torr pressure on these surfaces were performed. Thus, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al rectifier contact structures were obtained.

The I-V measurements of these three rectifier contact structures at room temperature were taken with "KEITLEY 2400 Picoammeter/ Voltage Source" device and the basic diode parameters were calculated.

#### **3** RESULTS AND DISCUSSION

In this section, InI-V graphs obtained from current-voltage measurements of Au/p-Si/Al, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al junctions will be given. In addition, rectification ratios of junctions, interface state densities and series resistance values will be calculated graphically from current-voltage measurements.

There are various current transport mechanisms for Schottky junction device. One of them is thermionic emission (TE) theory. According to this theory, only carriers with energies larger than the junction barrier  $\Phi b$  are able to overcome the Schottky barrier so these carriers contribute to the current voltage. The diode parameters including reverse saturation current (I<sub>0</sub>), ideality factor (n) and barrier height ( $\Phi_b$ ) were measured from the analysis of semilogarithmic I-V characteristic [6].

The ideal factor (n) can be calculated using the standard diode equation based on Schottky diode theory [7].

$$I = I_0 \left[ \exp\left(\frac{qv}{nkT}\right) - 1 \right] \tag{1}$$

where, I is the current through the diode, V is the voltage across the diode,  $I_0$  is the saturation current, n is the ideality factor, T is the absolute temperature in Kelvin, q is the electronic charge and k is Boltzmann constant.  $I_0$  is obtained from the straight line intercept of ln I at V = 0 and written as,

$$I_0 = AA^*T^2 \exp(-\frac{q\varphi_b}{kT})$$

<sup>(2)</sup>

where,  $\Phi$ b is the barrier height (eV) at zero bias, A is the diode area, A\* is the effective Richardson constant, n is ideality factor, which can be described as,

$$n = \frac{q}{kT} \frac{dV}{d(\ln I)} \tag{3}$$

where, dV/d(lnI) can be obtained from the linear region slope of ln (I) versus V plot. The barrier height can be calculated by using following formula,

$$\varphi_b = \frac{kT}{q} \ln\left(\frac{AA^*T^2}{I_0}\right) \tag{4}$$

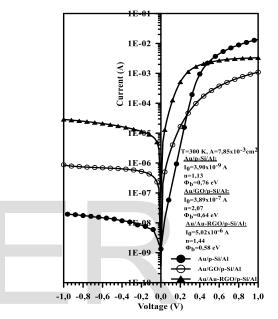

Figure 1 shows the lnI-V plots of Au / p-Si / Al, Au / GO / p-Si / Al and Au / Au-RGO / p-Si / Al juctions and with the help of these graphs, I0, n and  $\Phi$ b values calculated from the thermionic emission method are given.

Fig. 1. The forward and reverse bias In (I) -V graphs of Au/p-Si/AI, Au/GO/p-Si/AI and Au/Au-RGO/p-Si/AI junctions

According to Au / p-Si / Al reference structure, it is seen that the saturation current and ideality factor values increase of Au / GO / p-Si / Al and Au / Au-RGO / p-Si / Al structures and the barrier height values decrease.

It is well known that unless using ultra-high vacuum system, the fabricated Schottky barrier diodes possesses a thin interfacial native oxide layer between the metal and the semiconductor. The interface states and interfacial oxide layer at the metal semiconductor rectifying contact play an important role in the determination of the Schottky barrier diode and other characteristic parameters of the device and also affect the device performance [8]. For this reason, the addition of a non-naturally occurring interface layer to the metal and semiconductor interface clearly causes significant changes in diode parameters.

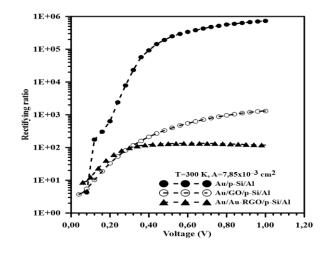

In Figure 2 and Figure 3, the rectifying ratios and interface state densities of Au/p-Si/Al, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al junctions are given respectively. As shown in Figure 2, the rectifying ratios also decreased due to the interface layer.

Fig. 2. The rectifying ratios of Au/p-Si/Al, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al junctions

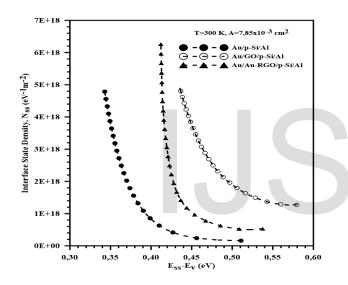

Fig. 3. The interface state densities of Au/p-Si/Al, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al junctions

As can be seen in Figure 3, the exponential growth of the interface-state density from midgap towards the top of the valence band is very apparent. It appears that the value of the interface state density does not change much depending on the interface layers.

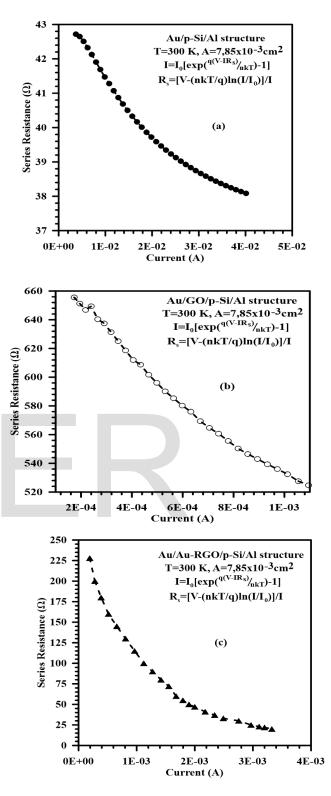

In metal semiconductor contacts, it plays an important role in determining the barrier height and ideality factor of the device in series resistance as well as the interface layer [9]. In Figure 4, series resistance changes with current of Au/p-Si/Al, Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al junctions are given.

Fig. 4. The series resistance of (a) Au/p-Si/AI, (b) Au/GO/p-Si/AI and (c) Au/Au-RGO/p-Si/AI junctions.

It is seen that the series resistance values increase with the interface layer and the diode parameters change accordingly [10].

## 4 CONCLUSIONS

In this study, Au / p-Si / Al reference metal semiconductor junction was obtained by thermal evaporation technique. Furthermore, GO and Au-RGO thin films were deposited as an interface layer between Au and p-Si by spin coating technique to obtain Au / GO / p-Si / Al and Au / Au-RGO / p-Si / Al structures. The diode parameters such as saturation current, ideality factor and barrier height were calculated by taking current voltage measurements at room temperature of the junctions obtained and these values were compared and interpreted.

As a result, it was seen that Au/GO/p-Si/Al and Au/Au-RGO/p-Si/Al structures exhibited their straightening characteristics and the electrical properties were examined and it was observed that the interface layer showed changes according to Au/p-Si/Al reference structure.

### REFERENCE

- B. Güzeldir, M. Sağlam, A. Ates, 2010 Analysis of the electrical characteristics of Zn/ZnSe/n-Si/Au-Sb structure fabricated using SILAR method as a function of temperature. Journal of Alloys and Compounds, 506 (2010) 388-394

- [2] B. Güzeldir, M. Sağlam, 2015. Temperature dependent electrical properties of Cd/CdS/n-Si/Au-Sb structures, Materials Science in Semiconductor Processing 30 (2015) 658–664.

- [3] O. Özakın, C. Aykaç, M. Odabas, A. Taşer, B. Güzeldir and M. Sağlam, 2018. A Study of Graphene Obtained by PECVD Technique Depending on RF Power, International Journal of Scientific & Engineering Research. Volume 9, Issue 5.

- [4] M. Cutroneo, V. Havranek, A. Mackova, P. Malinsky, L. Torrisi, L. Silipigni, B. Fazio, A. Torrisi, K. Szokolova, Z. Sofer, J. Stammers, 2019. Effects of the ion bombardment on the structure and composition of GO and rGO foils. Materials Chemistry and Physics 232 (2019) 272–277.

- [5] V. Maheskumar, I. Sheebh, B. Vidhyaa, J.P. Deebasree, T. Selvaraju, S. Akash, 2019. Enhanced electrocatalytic and photocatalytic activity of ball milled copper tin sulphide by incorporating GO and rGO, Applied Surface Science. 484 (2019) 265-275.

- [6] V. S. Rana, J. K. Rajput, T. K. Pathak, L.P. Purohit, 2019. Cu sputtered Cu/ZnO Schottky diodes on fluorine doped tin oxide substrate for optoelectronic applications, Thin Solid Films 679 (2019) 79-85.

- [7] A.B. Yadav, A. Pandey, D. Somvanshi, S. Jit, 2015. Sol-gel based highly sensitive Pd/nZnO thin film/n-Si schottky ultraviolet photodiodes, IEEE Trans. Electron Dev. 62 (2015) 1879-1884.

- [8] J. M. Dhimmar, H. N. Desai, B.P. Modi, 2016. The Effect of Interface States Density Distribution and Series Resistance on Electrical Behaviour of Schottky Diode Materials Today: Proceedings 3 (2016) 1658–1665.

- [9] A. Keffous, M. Siad, S. Mamma, Y. Belkacem, C. Lakhdar Chaouch, H. Menari, A. Dahmani, W. Chergui, 2003. Effect of series resistance on the performance of high resistivity silicon Schottky diode, Applied Surface Science 218 (2003) 336–342.

- [10] N. Singh, L. Kumar, A. Kumar, S. Vaisakh, S. Singh, K. Sisodiya, S. Srivastava, M. Kansal, S. Rawat, T. Singh, et al., Fabrication of zinc oxide/polyaniline (ZnO/ PANI) heterojunction and its characterisation at room temperature, Mater. Sci. Semicond. Process. 60 (2017) 29–33.